Update confidential designator here

# PC and the x86

Lesson 3

Fall 2024 FI MU

Rado Vrbovsky

<rvrbovsk@redhat.com>

- History of the computer

- IBM Personal Computer, model 5150

- PC architecture

- x86 CPU in a closer look

# History of the computer

#### History of the computer - Calculators - Ancient times

Roman Abacus

Zhusuan

Pascaline

Cash register

Curta

Mechanical calculators - source Wikipedia

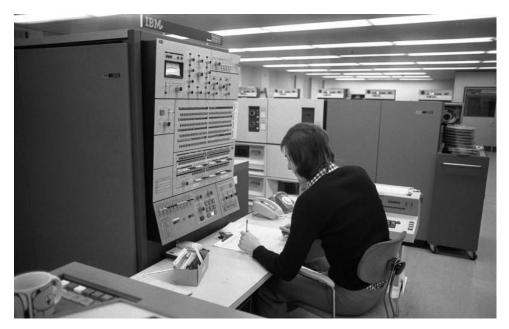

# Mainframe computer

- "The big iron"

- Large footprint (whole floor)

- Build for redundancy

- Large IO throughput (bulk data processing)

- Multiple OSes running at the same time in VMs

- Many modular peripherals

- Backward compatibility

- Used by US government, NASA, universities

- Still used today

### IBM System/360

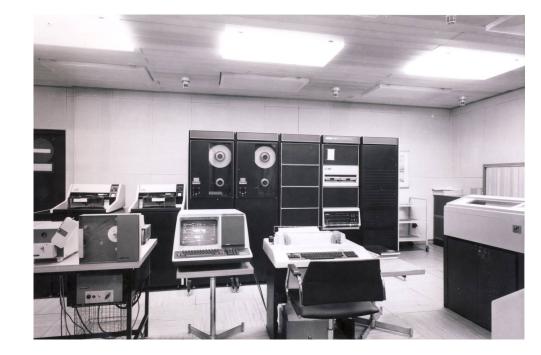

## Minicomputers

- 16/32 bit architecture

- Low cost version of a mainframe (but still size of a small truck or fridge)

- Eventually faded out

- Unix was written on DEC PDP-11

DEC PDP-11

## **Microcomputers**

- Small form factor

- Microchip CPU, 8 bit or 16 bit

- For home or office use

- Self assembled

- Single user

- Apple, Commodore, Tandy

- ČSSR Didaktik, PMD

Commodore - 64

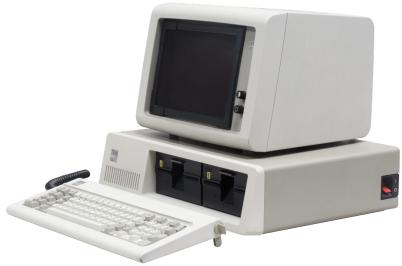

- Minicomputer market large enough to be noticed by IBM

- Super secret project inside IBM by a small team

- Use of "off the shelf" components

- Open hardware platform (ISA bus, option ROMs)

- Good open documentation including BIOS source code listing

IBM Personal Computer 5150

IBM Personal Computer - picture source Wikipedia

- Minicomputer market large enough to be noticed by IBM

- Super secret project inside IBM by a small team

- Use of "off the shelf" components

- Open hardware platform (ISA bus, option ROMs)

- Good open documentation including BIOS source code listing

- Easy to copy design -> Many cheap clones and 3rd party extension hardware -> Wide spread of platform

IBM hardware (set of chips)

- 8086 CPU

- 8237 DMA

- 8259 Interrupt controller

- 8253 Timer

- 6843 CRT controller

- 8042 Keyboard controller

- 8255 Cassette controller (PPI Programmable Peripheral Interface chip)

IBM hardware (set of chips)

- 8086 CPU

- 8237 DMA

- 8259 Interrupt controller

- 8253 Timer

- 6843 CRT controller

- 8042 Keyboard controller

- 8255 Cassette controller (PPI Programmable Peripheral Interface chip)

# Most of the hardware still present in some form.

IBM Personal Computer

- Fixed boot order

- When no bootable device was found, option ROM with BASIC was booted

- No interactive BIOS setup tool

- No resource management

- Manual assignment of resource by hand

- Conflicts hard to detect

- No power management

- Hard to make a portable device

## Jumper for HW configuration

# PC Architecture

#### PC Architecture - Historical Insight

Historical Insight

- Set of individual chips (8237, 8042, ...) integrated into one large component -> Chipset

- Later split again

- $\circ$  Speed

- Divide legacy hardware and the new PCI hardware

- Nowadays Memory Controller or the whole Northbridge controller integrated to CPU

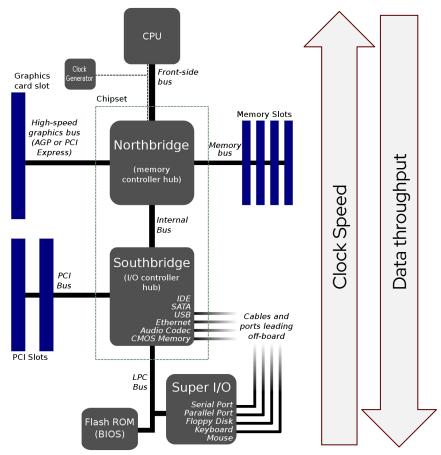

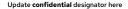

#### PC Architecture - Topology overview

Topology overview

List of nodes (devices) and links (buses) organized into a tree like structure

• Device

- A hardware component

- Storage device

- Human interface device

- CPU

- Bus bridge

- …

- Bus

- A communication system to transfer data between components inside a computer or between computers

- Bus attributes:

- Clock speed (Hz, MHz)

- Style (Parallel/Serial)

- Data width (8 bit, 16 bit, 32 bit, 64 bit, ...)

- Duplex (Half duplex, Full duplex)

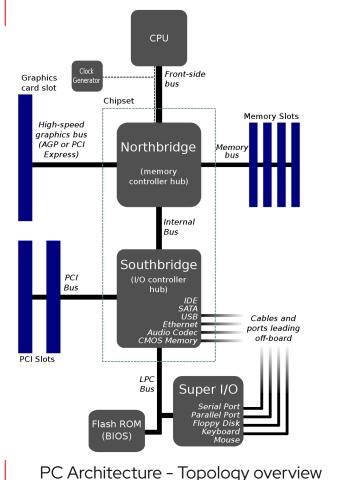

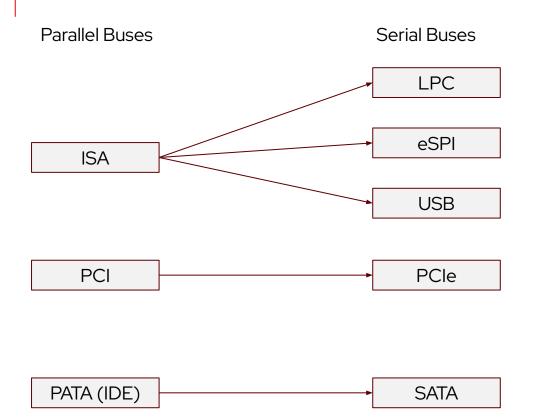

ISA - Industry Standard Architecture, (PC Bus or IO Channel)

- Original IBM PC Bus

- Used for expansion cards

- Peripheral devices

- Parallel, 8/16 bit, 4, 8 to 20Mhz

- DMA support

- 16 IRQ (cannot be shared and at least 6 were already used by internal devices)

- 12V, 5V

- All devices are equal

PCI - Peripheral Component Interconnect

- Intel 1992

- Replaces ISA

- Parallel, 32/64 bit, up to 66 MHz

- Tree like structure (up to 255 buses, each bus 32 devices, each device 8 functions (logical device))

- Shared IRQs among PCI devices, IRQs stolen from ISA

- 5V, 3V

- Software accessible configuration space with a vendor and a device ID and a class code

### AGP - Accelerated Graphics Port

- Intel 1997

- Parallel, 32 bit

- Specialized PCI bus for graphic card accelerators

PCIx - Peripheral Component Interconnect eXtended

- IBM, HP, and Compaq 1998

- Replaces PCI

- Parallel 32/64 bit, up to 533 MHz

- Hardware and software compatible with PCI

- Higher clock rates

PCIe - Peripheral Component Interconnect Express

- Intel, Dell, HP, IBM 2003

- Replaces PCI, AGP and PCIx

- High speed serial bus

- Not physically backward compatible

- Somewhat backward software compatible

LPC - Low Pin Count

- Intel 1994 as a substitute for ISA, 4 bit wide parallel

- Super IOs, BIOS ROM, Southbridge

eSPI - Enhanced Serial Peripheral Interface

- Substitute for LPC

- 1, 2, 4 bits wide

I2C - Inter-Integrated Circuit

- NXP in 1982

- 2 wire bus (SCL clock, SDA data)

- Sensors, EEPROMs, Fan control, EDID data in monitors and displays

SMBus - System Management Bus

- Intel and Duracell 1994

- Derived from I2C

- Used for motherboard devices, e.g. SPD (main memory configuration), laptop charging system (smart battery, embedded controller), sensors, fan, voltage regulator, clock generator

### USB - Universal Serial Bus

- Compaq, DEC, IBM, Intel, Microsoft, NEC, and Nortel 1996

- Standardize the connection of peripherals to computers

- Replacing UARTs, LPTs, game ports

- Nowadays support everything

ATA - AT Bus Attachment (Parallel ATA, IDE - Integrated Drive Electronics)

- Western digital and Compaq in 1986

- Direct connection to the 16 bit ISA bus for permanent storage (disks)

- Parallel

SATA - Serial AT Attachment

- 2000

- Substitute for PATA

- Higher data rates

- Native hot plug support

Over time width of bus is reduced from parallelism to serial.

WHY?

PC Architecture - Main PC Buses - Serialization of buses

Red Hat

- Reduces risk of clock skew

- Higher clock rates

- Easier PCB design and layout

- Saves space on PCB

- Lower production costs

### Firmware

- Hardware specific low level software

- CPU uCode, motherboard firmware, CDROMs, BT devices, hard drives, networking cards, graphic cards

- BIOS Basic I/O System

- PC specific firmware

- Resides in E, F segments

- POST Power On Self Test

- Boot up the computer

- Enumerate resources for present devices

- Scans for option ROMs

- Detects bootable devices

- Boots up the operating system

- Abstraction layer between hardware and the OS

- Provides runtime services for the OS

Legacy BIOS

- First IBM BIOS was very simple (fixed list of bootable devices, no HW or power management ...)

- Written in assembly language

UEFI - Unified Extensible Firmware Interface

- New standard since used 2010s

- Written mostly in C language

- Uses CAR (CPU Cache As Ram) for stack and heap before main memory is initialized

- Fully substitutes traditional BIOS, but can provide backward compatibility with Legacy BIOS if needed

- Modular

- Multiplatform (x86, ARM)

- Security by design

- Open Source implementations available

Many extensions since the first IBM BIOS

- BBS BIOS Boot Specification

- BIOS scans a list of bootable devices and lets user decide what to boot.

- DMI Desktop Management Interface

- Information about the hardware from specific vendors

- Information about the present hardware and its resources

- PNP Plug And Play

- Microsoft in the 90s

- PC was not aware of its own resources

- Per device configuration with resource profiles

- BIOS would find a suitable combination of profiles for all the devices

- BIOS would resolve resource conflicts

- APM Advanced Power Management

- Written by Microsoft and Intel in 1992

- APM BIOS is in charge of devices and platform as whole

- OS participates through APM driver and APM aware applications

- System and device states can be controlled either by BIOS or APM aware OS through BIOS

- ACPI Advanced Configuration and Power Interface

- Released by Microsoft, Intel and Toshiba in 1996

- All information about the hardware is provided through a single service

- OS is put in charge of the whole platform management

- Set of memory mapped tables containing information about the hardware

- AML ACPI Machine Language

- Bytecode containing all hardware specific routines for hardware

- Code in interpreted by the OS

## Interrupts (Traps)

- Started as an alternative to to polling

- Latency Delay between invoking (triggering, raising) and interrupt and running the software callback (handler)

- Can be masked (ignored) while running critical code

- Transparent to user space

## Hardware Interrupt (IRQs)

- Physical connection between a CPU and a device (SCSI, Net, Sound Card, ...)

- Serves as a notification from the device to the CPU

## Software Interrupt

- A callback function to handle a specific IRQ (interrupt handler)

- Can be also triggered by software by a special instruction

- 8086 had 256 interrupts, each interrupt mapped to a different callback

Interrupts, Exceptions, Traps - pictures source Wikipedia

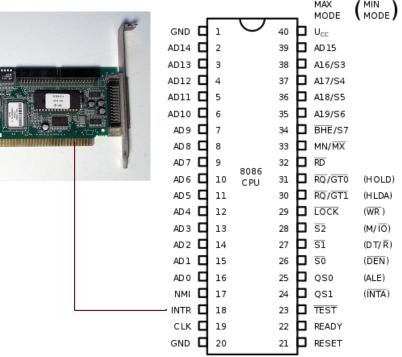

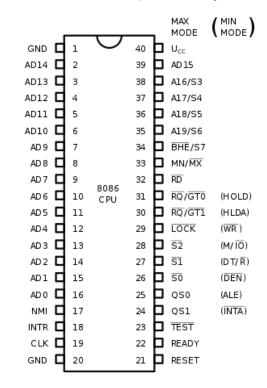

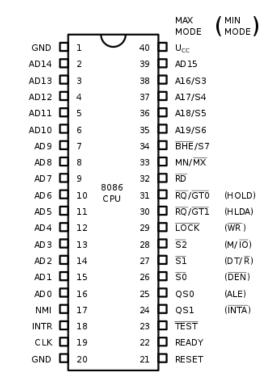

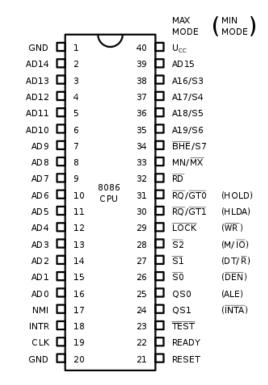

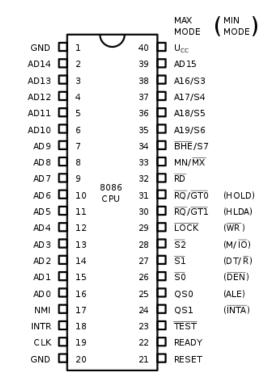

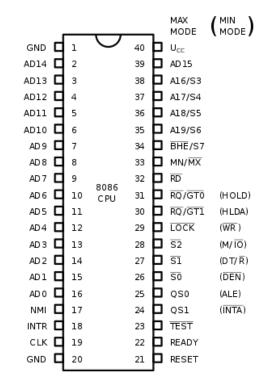

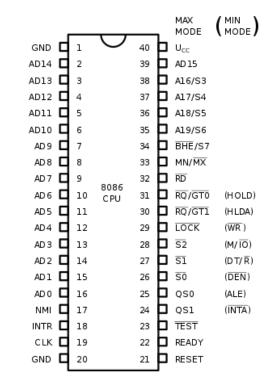

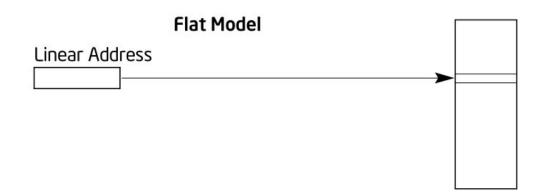

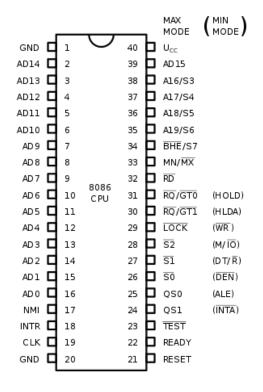

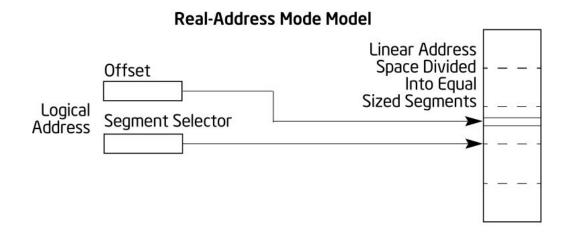

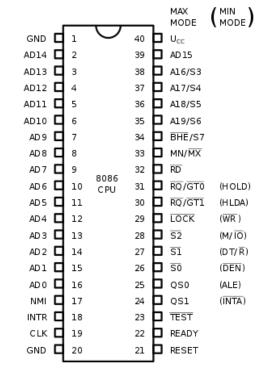

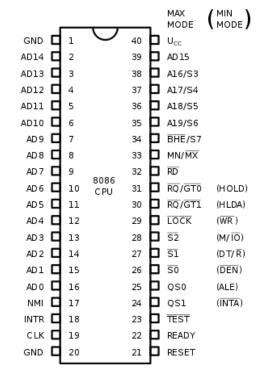

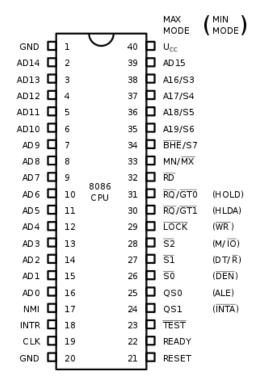

The 8086 pin assignments in min and max mode

| <ul> <li>Non Maskable Interrupts</li> <li>Like regular interrupts, but cannot be masked (ignored)</li> <li>Can occur while handling a different interrupt!</li> <li>Once NMI is handled, another cannot be serviced until IRET (Return from Interrupt) instruction is executed</li> <li>Used for critical events <ul> <li>Critical failure is eminent</li> <li>Data loss or data corruption</li> <li>Watchdog is triggered</li> </ul> </li> </ul> | GND 1<br>AD14 2<br>AD13 4<br>AD13 4<br>AD12 4<br>AD11 5<br>AD10 6<br>AD9 7<br>AD8 8<br>AD7 9<br>AD6 10 CPU<br>AD5 11<br>AD4 12<br>AD3 13<br>AD2 14<br>AD1 15<br>AD0 16<br>NMI 117 | MODE<br>40 U <sub>CC</sub><br>39 AD 15<br>38 AL6/S3<br>37 AL7/S4<br>36 AL8/S5<br>35 AL9/S6<br>34 BHE/S7<br>33 MN/MX<br>32 RD<br>5 31 RQ/GT0 (0<br>30 RQ/GT1 (0<br>29 CCCK (0<br>28 S2 (0<br>27 SI (0<br>26 S0 (0<br>25 QS0 (0 | HOLD)<br>HOLD)<br>HLDA)<br>WR)<br>DT/R)<br>DEN)<br>ALE)<br>INTA) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| <ul> <li>Internal CPU events</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           | → NMI <b>□</b> 17<br>INTR <b>□</b> 18                                                                                                                                             | 24 🗖 QS1 ()<br>23 🗖 TEST                                                                                                                                                                                                      | INTA)                                                            |

| <ul> <li>Processor-detected program-error exceptions (Faults, Traps,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   | CLK [] 19                                                                                                                                                                         | 22 D READY                                                                                                                                                                                                                    |                                                                  |

| Aborts)                                                                                                                                                                                                                                                                                                                                                                                                                                           | GND 🗖 20                                                                                                                                                                          | 21 RESET                                                                                                                                                                                                                      |                                                                  |

Software-generated exceptions (INT 0, INT 1, INT3)

• Machine-check exceptions

The 8086 pin assignments in min and max mode

Interrupts, Exceptions, Traps - pictures source Wikipedia

# DMA - Direct Memory Access

- Copy data over address space without involving CPU (its too slow for that anyway)

- DMA controller device that copies the data over memory address bus

- Used mainly by devices (network cards, sound cards, storage devices, video cards, ...)

- DMA16 16bit legacy address space used by ISA cards

- DMA32 32bit address space for PCI devices

|      |   |    | <u> </u>   |    |   | MAX<br>MODE        | (MIN<br>MODE) |

|------|---|----|------------|----|---|--------------------|---------------|

| GND  | þ | 1  | $\bigcirc$ | 40 | Þ | Ucc                |               |

| AD14 | þ | 2  |            | 39 | Þ | AD 15              |               |

| AD13 | q | 3  |            | 38 | Þ | A16/S3             |               |

| AD12 | q | 4  |            | 37 | Þ | A17/S4             |               |

| AD11 | þ | 5  |            | 36 | Þ | A18/S5             |               |

| AD10 | q | 6  |            | 35 | Þ | A19/S6             |               |

| AD 9 | q | 7  |            | 34 | Þ | BHE/S7             |               |

| AD 8 | q | 8  |            | 33 | Þ | $MN/\overline{MX}$ |               |

| AD 7 | q | 9  | 8086       | 32 | Þ | RD                 |               |

| AD 6 | q | 10 | CPU        | 31 | Þ | RQ/GT0             | (HOLD)        |

| AD 5 | þ | 11 |            | 30 | Þ | RQ/GT1             | (HLDA)        |

| AD 4 | q | 12 |            | 29 | Þ | LOCK               | (WR)          |

| AD 3 | q | 13 |            | 28 | Þ | S2                 | (M/ 10)       |

| AD 2 | q | 14 |            | 27 | Þ | <u>51</u>          | (D T/ R)      |

| AD 1 | q | 15 |            | 26 | Þ | S0                 | (DEN)         |

| AD 0 | q | 16 |            | 25 | Þ | QS0                | (ALE)         |

| NMI  | q | 17 |            | 24 | Þ | QS1                | (INTA)        |

| INTR | q | 18 |            | 23 | Þ | TEST               |               |

| CLK  | q | 19 |            | 22 | Þ | READY              |               |

| GND  | q | 20 |            | 21 | þ | RESET              |               |

The 8086 pin assignments in min and max mode

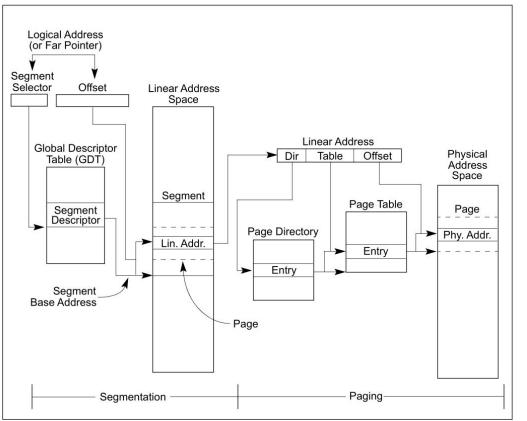

# x86 CPU in a closer look

#### Update confidential designator here

| MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (MODE)   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Architecture and features ${}_{\text{GND}} \mathbf{q}_{1} \bigvee_{40} \mathbf{p}_{\text{U}_{cc}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| CISC - Complex Instruction Set Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| Instruction Pipelining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| Superscalar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| Speculative Execution     AD 8     AD 8 |          |

| • Branch Prediction AD 6 🖬 10 8086 31 🗖 RQ/GT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ) (HOLD) |

| <ul> <li>Out of Order Execution</li> <li>AD5 9 11 30 8 RQ/GT</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| AD4 🗖 12 29 🗖 LOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (WR)     |

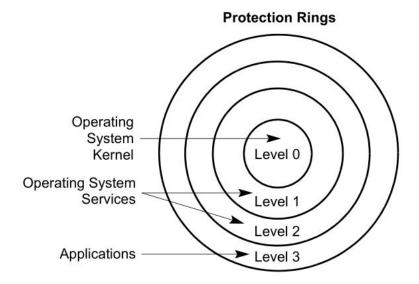

| Privilege modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (M/ 10)  |

| • CPU modes 4D2 27 2 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (D T/ R) |

| $AD1 = 15 \qquad 26 = \overline{50}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (DEN)    |

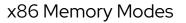

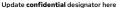

| Memory modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (ALE)    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (INTA)   |

| Interrupts and Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| Registers     GND Q 20 21 RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

The 8086 pin assignments in min and max mode

### x86 CPU

CISC - Complex Instruction Set Computer

- Single instructions can execute several low-level operations • (such as a load from memory, an arithmetic operation, and a memory store)

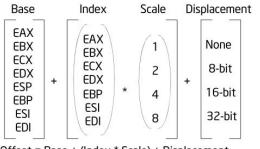

- add rax,QWORD PTR [rbx+rbp\*8+0xa] Intel:

- AT&T: add 0xa(%rbx,%rbp,8),%rax

The 8086 pin assignments in min and max mode

CISC - Complex Instruction Set Computer

Single instructions can execute several low-level operations (such as a load from memory, an arithmetic operation, and a memory store)

| Intel: | add | rax,QWORD | PTR | [rbx+rbp*8+0xa] |

|--------|-----|-----------|-----|-----------------|

|--------|-----|-----------|-----|-----------------|

AT&T: add 0xa(%rbx, %rbp, 8), %rax

Offset = Base + (Index \* Scale) + Displacement

Multiply register and constant

Add result with a constant

- 3. Add result with a register

- 4. Fetch QWORD from memory

- 5. Add register and a constant

- 6. Store result in a register

The 8086 pin assignments in min and max mode

| Update | confidential | designator here |

|--------|--------------|-----------------|

|--------|--------------|-----------------|

|                                                                                   |                |             | MAX<br>MODE | (MIN<br>MODE) |

|-----------------------------------------------------------------------------------|----------------|-------------|-------------|---------------|

| CISC - Complex Instruction Set Computer                                           | GND 🗗 1 💛      | ′₄₀Þ        | Ucc         |               |

| <ul> <li>Variable length of instructions</li> </ul>                               | AD14 🗖 2       | 39 <b>þ</b> | AD 15       |               |

| Variable length of instructions                                                   | AD13 🗖 3       | 38 Þ        | A16/S3      |               |

| <ul> <li>Instructions take several CPU cycles to execute, depending on</li> </ul> | AD12 🗖 4       | 37 Þ        | A17/S4      |               |

| the instructions and its operands                                                 | AD11 🗖 5       | 36 Þ        | A18/S5      |               |

| the instructions and its operatios                                                | AD10 🗖 6       | 35 Þ        | A19/S6      |               |

|                                                                                   | AD 9 🗖 7       | 34 Þ        | BHE/S7      |               |

| Intel: 48 c7 45 f8 78 56 34 12 mov _QWORD PTR [rbp-0x8], 0x12345678               | AD 8 🗖 8       | 33 Þ        | MN/MX       |               |

|                                                                                   | AD 7 🗖 9       | 32 🗗        | RD          |               |

| c3 ret                                                                            | AD 6 🗖 10 8086 | 31 Þ        | RQ/GT0      | (HOLD)        |

|                                                                                   | AD5 🗖 11       | 30 Þ        | RQ/GT1      | (HLDA)        |

|                                                                                   | AD4 🗖 12       | 29 뉟        | LOCK        | (WR)          |

| AT&T: 48 c7 45 f8 78 56 34 12 movg \$0x12345678,-0x8(%rbp)                        | AD 3 🗖 13      | 28 Þ        | S2          | (M/10)        |

|                                                                                   | AD 2 🗖 14      | 27 Þ        | SI          | (D T/ R)      |

| c3 ret                                                                            | AD1 🗖 15       | 26 Þ        | S0          | (DEN)         |

|                                                                                   | AD 0 🗖 16      | 25 🗖        | QS0         | (ALE)         |

- Great for assembler developers (and virus writers)

- Nightmare for CPU designers (x86 is backward compatible to 1978) .

- Modern x86 CPUs are internally RISC (Reduced Instruction Set • Computers), CISC instructions are translated to RISC instructions internally

The 8086 pin assignments in min and max mode

24 051

23 D TEST

22 п READY

21

RESET

(INTA)

**D** 17

**D** 18

**D** 19

**D** 20

NMI

INTR

CLK

GND

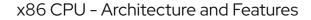

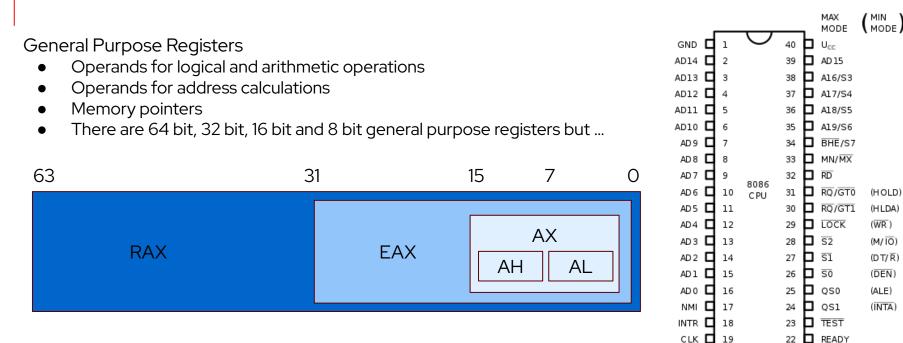

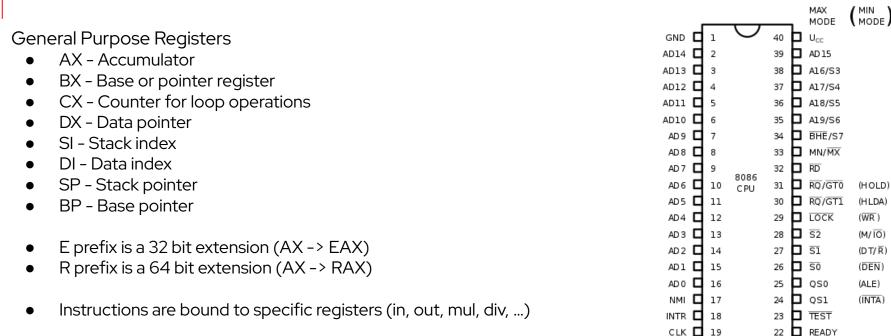

#### x86 CPU - Architecture and Features

Little Endian

• Order in which bytes are stored in computer memory

unsigned long value = 0x12345678;

| Offset | Little Endian | Big Endian |

|--------|---------------|------------|

| 0x1000 | 0x78          | 0x12       |

| 0x1001 | 0x56          | 0x34       |

| 0x1002 | 0x34          | Øx56       |

| 0x1003 | 0x12          | 0x78       |

- BE From historical architectures like IBM, still used by networking protocols

- LE Simplifies silicon design and arithmetic operations on integers

The 8086 pin assignments in min and max mode

x86 CPU - Architecture and Features

ID

EX

MEM

WB

Instruction Pipelining

Z 1.4181

|            |          |          |           |          |          |          |          |         |         |        |    |             |    |    | MAX<br>MODE | (MIN<br>MODE) |

|------------|----------|----------|-----------|----------|----------|----------|----------|---------|---------|--------|----|-------------|----|----|-------------|---------------|

| uction     | Pipelin  | ning     |           |          |          |          |          |         |         | GND 🕻  | 1  | $\bigcirc$  | 40 | þ  | Ucc         | . ,           |

| Idea o     | riainat  | ed in R  | RISC CF   |          | ians     |          |          |         |         | AD14 🕻 | 2  |             | 39 | 2  | AD 15       |               |

|            | 0        |          |           |          | 0        |          |          |         |         | AD13   | 3  |             | 38 | Ρ  | A16/S3      |               |

| Split e    | xecutio  | on of ir | nstruct   | ions int | to stag  | es       |          |         |         | AD12   | 4  |             | 37 | P  | A17/S4      |               |

|            | instru   | ction c  | an be p   | roces    | sed wh   | nile nre | vious ir | nstruct | tion is | AD11 🕻 | 5  |             | 36 | P  | A18/S5      |               |

|            |          |          | •         |          |          | •        |          | Suuci   |         | AD10 🕻 | 6  |             | 35 | ρ. | A19/S6      |               |

| being      | proces   | ssed in  | a later   | stage    | of the   | pipelin  | e        |         |         | AD 9   | 7  |             | 34 | ρ  | BHE/S7      |               |

| Simpli     | fies CF  |          | ian       | •        |          |          |          |         |         | AD 8 🕻 | 8  |             | 33 | Þ  | MN/MX       |               |

| •          |          |          | 5         |          |          |          |          |         |         | AD 7 🕻 | 9  | 0000        | 32 | Þ  | RD          |               |

| Makes      | s sure e | each pa  | art of th | he CPl   | J is bus | sy       |          |         |         | AD 6   | 10 | 8086<br>CPU | 31 | Þ  | RQ/GT0      | (HOLD)        |

|            |          |          |           |          |          |          |          |         |         | AD 5   | 11 |             | 30 | ρ  | RQ/GT1      | (HLDA)        |

| IF         | ID       | ΕX       | MEM       | WB       |          |          |          |         |         | AD4 🕻  | 12 |             | 29 | Þ  | LOCK        | (WR)          |

|            |          |          |           |          |          |          |          |         |         | AD 3   | 13 |             | 28 | Ρ  | S2          | (M/ 10)       |

| ļi         | IF       | ID       | EX        | MEM      | WB       |          |          |         |         | AD 2   | 14 |             | 27 | Þ  | SI          | (D T/ R)      |

| t          |          | IF       | ID        | ΕX       | MEM      | WB       |          |         |         | AD1    | 15 |             | 26 | Ρ  | S0          | (DEN)         |

| <b>-</b> → | ļ        |          |           |          |          |          |          |         |         | AD 0   | 16 |             | 25 | P  | QS0         | (ALE)         |

|            |          |          | IF        | ID       | ΕX       | MEM      | WB       |         |         | NMI 🕻  | 17 |             | 24 | P  | QS1         | (INTA)        |

|            |          |          |           | 10       |          | ΓV       | NALINA   |         | ]       | INTR 🕻 | 18 |             | 23 | Þ  | TEST        |               |

Basic five-stage pipeline in a RISC machine (IF = Instruction Fetch, ID = Instruction Decode, EX = Execute, MEM = Memory access, WB = Register write back)

The 8086 pin assignments in min and max mode

22 п READY

21 RESET

CLK

GND

**D** 19

20

Speculative Execution - Branch Prediction

- On conditional branching, the CPU starts to execute both branches without knowing the result (using separate pipelines).

Upon knowing the result, the pipeline with wrong chosen path is flushed

- Reduces risk of choosing the wrong code branch of execution and refilling the whole pipeline

```

int do_stuff(int a, int b)

{

if (a > b)

goto _exit;

printf("Hello world!\n");

return 1;

_exit:

return 0;

}

```

The 8086 pin assignments in min and max mode

x86 CPU - Architecture and Features

xkcd.com

- Yes, there was a goto in the last example.

- The kernel code is full of them.

- A goto generates a relative jump and branch predictor makes sure that at least one pipeline is not completely flushed.

- Absolute jumps flush instruction pipeline completely.

Speculative Execution - Out of order execution

- The CPU executes instructions in a order depending on the availability of pipelines, disregarding order of instructions in the program

- Reduces idleness of pipelines

| Intel: | mo∨<br>add | rax,QWORD PTR [rbx<br>rcx,rdx |

|--------|------------|-------------------------------|

| AT&T:  | mo∨<br>add | (%rbx),%rax<br>%rdx,%rcx      |

Speculative Execution - Out of order execution

- The CPU executes instructions in a order depending on the availability of pipelines, disregarding order of instructions in the program

- Reduces idleness of pipelines

| Intel: | mo∨<br>add | rax,QWORD PTR [rbx]<br>rcx,rdx |

|--------|------------|--------------------------------|

| AT&T:  | mo∨<br>add | (%rbx),%rax<br>%rdx,%rcx       |

The addition will be executed first. It is not dependent on result of previous operation. Fetch from memory is guaranteed to take longer than addition on registers.

| Register       AD14       1       40       Ucc         • Device specific storage       AD13       3       38       AL6/S3         AD12       4       37       AL7/S4         AD10       6       5       6       AL9/S5         AD10       6       5       AL9/S5         AD10       6       5       AL9/S5         AD10       6       5       AL9/S5         AD10       6       5       AL9/S5         Segment Registers       AD1       6       5         Flag Register       AD6       1       80         Instruction Pointer Registers       AD2       7       34         Octortrol Registers       AD2       10       R0/GT       (HoLD)         Memory Registers       AD3       13       28       52       (MT0)         PU Registers       AD2       14       27       51       (DTR)         Registers For Multimedia Extensions       AD1       15       26       50       (MTR)         Debug Registers       CLK       19       22       READY       (MTR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  |        |    |            |    | MAX<br>MODE | (MIN<br>MODE) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|----|------------|----|-------------|---------------|

| <ul> <li>Device specific storage</li> <li>Als/53</li> <li>Als/53</li> <li>Als/53</li> <li>Als/53</li> <li>Als/53</li> <li>Als/53</li> <li>Als/53</li> <li>Als/53</li> <li>Als/54</li> <li>AD11</li> <li>5</li> <li>36</li> <li>Als/55</li> <li>Als/56</li> <li>Als/55</li> <li>Als/56</li> <li>Als/55</li> <li>Als/55</li> <li>Als/55&lt;</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  | GND 🛛  | 1  | $\bigcirc$ | 40 |             |               |

| AD22437A17/54AD10536A18/55AD10635A19/56General Purpose RegistersAD9734BHE/57Segment RegistersAD79833MN/MXFlag RegisterAD610832R0Instruction Pointer RegistersAD6108001130R0/GT0Instruction Pointer RegistersAD61130R0/GT0(HoLD)Ocntrol RegistersAD61130S2S2(WR)Memory RegistersAD61328S2(WR)FPU RegistersAD7152650(DT/R)Put RegistersAD7111526S0(DT/R)Debug RegistersAD7111229R0/GT0(INTA)Debug RegistersNMI1724QS1(INTA)NMI1724QS1TESTTESTCIK1922READYTESTTEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Register                                         | AD14 🕻 | 2  |            | 39 | 🗖 AD 15     |               |